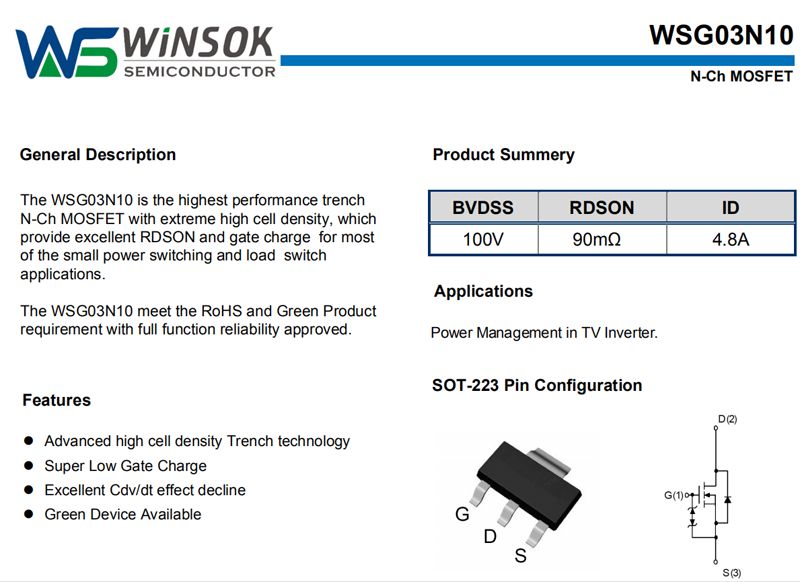

"MOSFET" yw'r talfyriad o Transistor Effaith Maes Lled-ddargludyddion Metal Ocsid. Mae'n ddyfais wedi'i gwneud o dri deunydd: metel, ocsid (SiO2 neu SiN) a lled-ddargludyddion. MOSFET yw un o'r dyfeisiau mwyaf sylfaenol yn y maes lled-ddargludyddion. P'un a yw mewn dylunio IC neu gymwysiadau cylched lefel bwrdd, mae'n helaeth iawn. Mae prif baramedrau MOSFET yn cynnwys ID, IDM, VGSS, V(BR) DSS, RDS(on), VGS(th), ac ati. Ydych chi'n gwybod y rhain? OLUKEY Cwmni, fel winsok Taiwanese canol-i-uchel-diwedd canolig ac isel-folteddMOSFETdarparwr gwasanaeth asiant, mae ganddo dîm craidd gyda bron i 20 mlynedd o brofiad i egluro i chi yn fanwl baramedrau amrywiol MOSFET!

Disgrifiad o ystyr paramedrau MOSFET

1. Paramedrau eithafol:

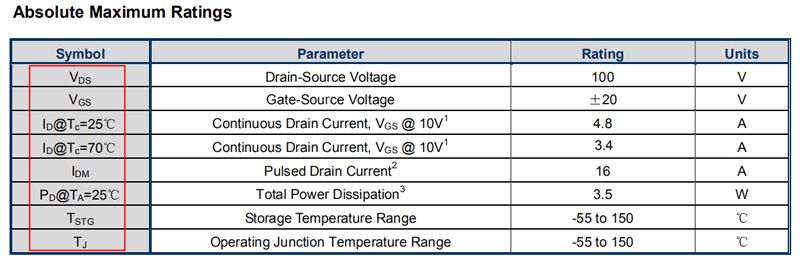

ID: Uchafswm cerrynt ffynhonnell draen. Mae'n cyfeirio at yr uchafswm cerrynt a ganiateir i basio rhwng y draen a'r ffynhonnell pan fydd y transistor effaith maes yn gweithredu'n normal. Ni ddylai cerrynt gweithredu'r transistor effaith maes fod yn fwy na'r ID. Mae'r paramedr hwn yn gostwng wrth i dymheredd y gyffordd gynyddu.

IDM: Uchafswm cerrynt ffynhonnell draen pwls. Bydd y paramedr hwn yn gostwng wrth i dymheredd y gyffordd gynyddu, gan adlewyrchu ymwrthedd effaith ac mae hefyd yn gysylltiedig ag amser pwls. Os yw'r paramedr hwn yn rhy fach, efallai y bydd y system mewn perygl o gael ei thorri i lawr gan gerrynt yn ystod profion OCP.

PD: Uchafswm pŵer wedi'i wasgaru. Mae'n cyfeirio at yr uchafswm afradu pŵer ffynhonnell draen a ganiateir heb ddirywio perfformiad y transistor effaith maes. Pan gaiff ei ddefnyddio, dylai defnydd pŵer gwirioneddol y FET fod yn llai na defnydd y PDSM a gadael ymyl penodol. Mae'r paramedr hwn yn gostwng yn gyffredinol wrth i dymheredd y gyffordd gynyddu

VDSS: Uchafswm draen-ffynhonnell wrthsefyll foltedd. Y foltedd ffynhonnell draen pan fydd y cerrynt draen sy'n llifo yn cyrraedd gwerth penodol (ymchwydd yn sydyn) o dan gylched byr tymheredd a phorthladd penodol. Gelwir y foltedd ffynhonnell draen yn yr achos hwn hefyd yn foltedd chwalu eirlithriadau. Mae gan VDSS gyfernod tymheredd positif. Ar -50 ° C, mae VDSS tua 90% o hynny ar 25 ° C. Oherwydd y lwfans a adewir fel arfer mewn cynhyrchiad arferol, mae foltedd chwalu eirlithriadau MOSFET bob amser yn fwy na'r foltedd graddedig enwol.

OLUKEYAwgrymiadau Cynnes: Er mwyn sicrhau dibynadwyedd cynnyrch, o dan yr amodau gwaith gwaethaf, argymhellir na ddylai'r foltedd gweithio fod yn fwy na 80 ~ 90% o'r gwerth graddedig.

VGSS: Uchafswm porth-ffynhonnell wrthsefyll foltedd. Mae'n cyfeirio at y gwerth VGS pan fydd y cerrynt gwrthdro rhwng y giât a'r ffynhonnell yn dechrau cynyddu'n sydyn. Bydd mynd y tu hwnt i'r gwerth foltedd hwn yn achosi dadansoddiad dielectrig o'r haen giât ocsid, sy'n chwalfa ddinistriol ac anwrthdroadwy.

TJ: Uchafswm tymheredd gweithredu cyffordd. Fel arfer mae'n 150 ℃ neu 175 ℃. O dan amodau gwaith dylunio dyfais, mae angen osgoi mynd y tu hwnt i'r tymheredd hwn a gadael ymyl penodol.

TSTG: ystod tymheredd storio

Mae'r ddau baramedr hyn, TJ a TSTG, yn graddnodi'r ystod tymheredd cyffordd a ganiateir gan amgylchedd gweithio a storio'r ddyfais. Mae'r amrediad tymheredd hwn wedi'i osod i fodloni gofynion bywyd gweithredu lleiaf y ddyfais. Os sicrheir bod y ddyfais yn gweithredu o fewn yr ystod tymheredd hwn, bydd ei fywyd gwaith yn cael ei ymestyn yn fawr.

2. Paramedrau statig

Yn gyffredinol, amodau prawf MOSFET yw 2.5V, 4.5V, a 10V.

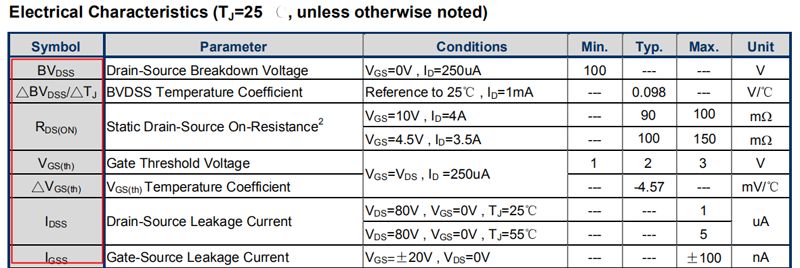

V(BR) DSS: Foltedd dadansoddi ffynhonnell draen. Mae'n cyfeirio at y foltedd ffynhonnell draen uchaf y gall y transistor effaith maes ei wrthsefyll pan fo foltedd ffynhonnell giât VGS yn 0. Mae hwn yn baramedr cyfyngu, a rhaid i'r foltedd gweithredu a roddir ar y transistor effaith maes fod yn llai na V(BR). DSS. Mae ganddo nodweddion tymheredd cadarnhaol. Felly, dylid cymryd gwerth y paramedr hwn o dan amodau tymheredd isel fel ystyriaeth diogelwch.

△V(BR) DSS/△Tj: Cyfernod tymheredd foltedd dadelfennu ffynhonnell draen, yn gyffredinol 0.1V / ℃

RDS (ymlaen): O dan rai amodau VGS (10V fel arfer), tymheredd cyffordd a cherrynt draen, y gwrthiant mwyaf rhwng y draen a'r ffynhonnell pan fydd y MOSFET yn cael ei droi ymlaen. Mae'n baramedr pwysig iawn sy'n pennu'r pŵer a ddefnyddir pan fydd y MOSFET yn cael ei droi ymlaen. Mae'r paramedr hwn yn cynyddu'n gyffredinol wrth i dymheredd y gyffordd gynyddu. Felly, dylid defnyddio gwerth y paramedr hwn ar y tymheredd cyffordd gweithredu uchaf ar gyfer cyfrifo colled a gostyngiad foltedd.

VGS(th): foltedd troi ymlaen (foltedd trothwy). Pan fydd foltedd rheoli'r giât allanol VGS yn fwy na VGS(th), mae haenau gwrthdroad arwyneb y draeniau a'r rhanbarthau ffynhonnell yn ffurfio sianel gysylltiedig. Mewn cymwysiadau, gelwir y foltedd giât pan fydd ID yn hafal i 1 mA o dan gyflwr cylched byr y draen yn aml yn foltedd troi ymlaen. Mae'r paramedr hwn yn gostwng yn gyffredinol wrth i dymheredd y gyffordd gynyddu

IDSS: cerrynt ffynhonnell draen dirlawn, y cerrynt ffynhonnell draen pan fo foltedd adwy VGS=0 a VDS yn werth penodol. Yn gyffredinol ar lefel microamp

IGSS: cerrynt gyriant ffynhonnell gât neu gerrynt gwrthdro. Gan fod rhwystriant mewnbwn MOSFET yn fawr iawn, mae IGSS yn gyffredinol yn y lefel nanoamp.

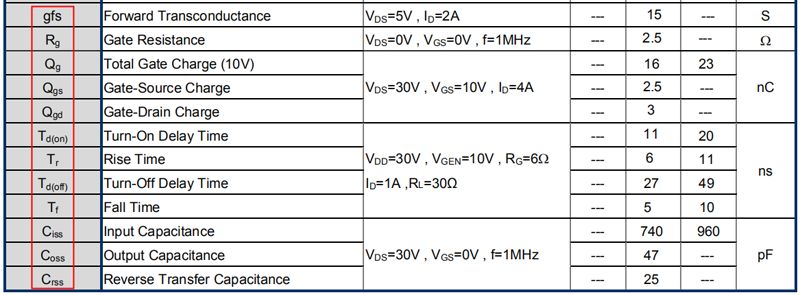

3. paramedrau deinamig

gfs: trawsgludo. Mae'n cyfeirio at gymhareb y newid mewn cerrynt allbwn draen i'r newid mewn foltedd ffynhonnell giât. Mae'n fesur o allu foltedd ffynhonnell giât i reoli cerrynt draen. Edrychwch ar y siart ar gyfer y berthynas drosglwyddo rhwng gfs a VGS.

Qg: Cyfanswm capasiti codi tâl giât. Dyfais gyrru math foltedd yw MOSFET. Y broses yrru yw'r broses sefydlu foltedd giât. Cyflawnir hyn trwy wefru'r cynhwysedd rhwng ffynhonnell y giât a draen giât. Bydd yr agwedd hon yn cael ei thrafod yn fanwl isod.

Qgs: Gât ffynhonnell codi tâl capasiti

Qgd: tâl giât-i-draen (gan gymryd i ystyriaeth effaith Miller). Dyfais gyrru math foltedd yw MOSFET. Y broses yrru yw'r broses sefydlu foltedd giât. Cyflawnir hyn trwy wefru'r cynhwysedd rhwng ffynhonnell y giât a draen giât.

Td (ymlaen): amser oedi dargludiad. Yr amser o pan fydd y foltedd mewnbwn yn codi i 10% nes bod VDS yn disgyn i 90% o'i osgled

Tr: amser codi, yr amser i'r foltedd allbwn VDS ostwng o 90% i 10% o'i osgled

Td (i ffwrdd): Amser oedi diffodd, yr amser o'r amser pan fydd y foltedd mewnbwn yn disgyn i 90% hyd pan fydd VDS yn codi i 10% o'i foltedd diffodd

Tf: Amser cwympo, yr amser i'r foltedd allbwn VDS godi o 10% i 90% o'i osgled

Ciss: Cynhwysedd mewnbwn, cylched byr y draen a'r ffynhonnell, a mesurwch y cynhwysedd rhwng y giât a'r ffynhonnell gyda signal AC. Ciss = CGD + CGS (cylched byr CDS). Mae'n cael effaith uniongyrchol ar oedi troi ymlaen a diffodd y ddyfais.

Cost: Cynhwysedd allbwn, cylched byr y giât a'r ffynhonnell, a mesurwch y cynhwysedd rhwng y draen a'r ffynhonnell gyda signal AC. Coss = CDS + CGD

Crss: Cynhwysedd trosglwyddo gwrthdro. Gyda'r ffynhonnell wedi'i chysylltu â'r ddaear, mae'r cynhwysedd wedi'i fesur rhwng y draen a'r giât Crss = CGD. Un o'r paramedrau pwysig ar gyfer switshis yw'r amser codi a chwympo. Crss=CGD

Mae cynhwysedd rhyng-electrod a chynhwysedd a achosir gan MOSFET MOSFET yn cael eu rhannu'n gynhwysedd mewnbwn, cynhwysedd allbwn a chynhwysedd adborth gan y rhan fwyaf o weithgynhyrchwyr. Mae'r gwerthoedd a ddyfynnir ar gyfer foltedd sefydlog draen-i-ffynhonnell. Mae'r cynhwysedd hyn yn newid wrth i'r foltedd ffynhonnell draen newid, ac mae gwerth y cynhwysedd yn cael effaith gyfyngedig. Nid yw'r gwerth cynhwysedd mewnbwn ond yn rhoi syniad bras o'r tâl sy'n ofynnol gan gylched y gyrrwr, tra bod gwybodaeth gwefru'r giât yn fwy defnyddiol. Mae'n nodi faint o ynni y mae'n rhaid i'r giât ei godi i gyrraedd foltedd penodol o'r giât i'r ffynhonnell.

4. Avalanche dadansoddiad paramedrau nodweddiadol

Mae'r paramedr nodweddiadol dadansoddiad eirlithriadau yn ddangosydd o allu'r MOSFET i wrthsefyll gorfoltedd yn y cyflwr oddi arno. Os yw'r foltedd yn fwy na'r foltedd terfyn ffynhonnell draen, bydd y ddyfais mewn cyflwr eirlithriad.

EAS: Egni chwalu eirlithriad pwls sengl. Mae hwn yn baramedr terfyn, sy'n nodi'r uchafswm egni chwalu eirlithriadau y gall y MOSFET ei wrthsefyll.

IAR: cerrynt eirlithriadau

YAG: Egni Toriad Avalanche Ailadrodd

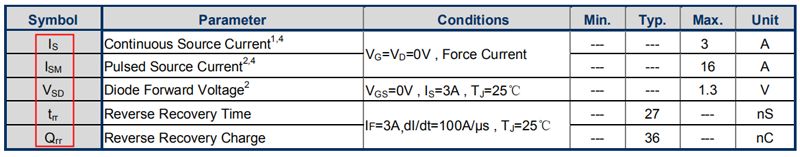

5. Paramedrau deuod in vivo

YW: Cerrynt rhydd-olwyn uchaf parhaus (o'r ffynhonnell)

ISM: cerrynt rhydd-olwyn uchaf curiad y galon (o'r ffynhonnell)

VSD: gostyngiad foltedd ymlaen

Trr: amser adfer gwrthdroi

Qrr: Adfer tâl gwrthdro

Ton: Ymlaen amser dargludiad. (Dibwys yn y bôn)

Amser troi ymlaen MOSFET a diffiniad amser troi i ffwrdd

Yn ystod y broses ymgeisio, yn aml mae angen ystyried y nodweddion canlynol:

1. Nodweddion cyfernod tymheredd cadarnhaol V (BR) DSS. Mae'r nodwedd hon, sy'n wahanol i ddyfeisiau deubegwn, yn eu gwneud yn fwy dibynadwy wrth i dymheredd gweithredu arferol gynyddu. Ond mae angen i chi hefyd roi sylw i'w ddibynadwyedd yn ystod cychwyniadau oer tymheredd isel.

2. Nodweddion tymheredd negyddol cyfernod V(GS)th. Bydd potensial trothwy'r giât yn gostwng i raddau wrth i dymheredd y gyffordd gynyddu. Bydd rhywfaint o ymbelydredd hefyd yn lleihau'r potensial trothwy hwn, o bosibl hyd yn oed o dan 0 potensial. Mae'r nodwedd hon yn ei gwneud yn ofynnol i beirianwyr roi sylw i ymyrraeth a sbarduno ffug MOSFETs yn y sefyllfaoedd hyn, yn enwedig ar gyfer cymwysiadau MOSFET sydd â photensial trothwy isel. Oherwydd y nodwedd hon, weithiau mae angen dylunio potensial all-foltedd gyrrwr y giât i werth negyddol (gan gyfeirio at N-math, P-math ac yn y blaen) er mwyn osgoi ymyrraeth a sbarduno ffug.

3. Nodweddion cyfernod tymheredd positif VDSon/RDSo. Mae'r nodwedd bod VDSon/RDSon yn cynyddu ychydig wrth i dymheredd y gyffordd gynyddu yn ei gwneud hi'n bosibl defnyddio MOSFETs yn uniongyrchol ochr yn ochr. Mae dyfeisiau deubegwn i'r gwrthwyneb yn hyn o beth, felly mae eu defnydd ochr yn ochr yn dod yn eithaf cymhleth. Bydd RDSon hefyd yn cynyddu ychydig wrth i ID gynyddu. Mae'r nodwedd hon a nodweddion tymheredd positif RDSon cyffordd ac arwyneb yn galluogi MOSFET i osgoi dadansoddiad eilaidd fel dyfeisiau deubegwn. Fodd bynnag, dylid nodi bod effaith y nodwedd hon yn eithaf cyfyngedig. Pan gaiff ei ddefnyddio ar y cyd, gwthio-tynnu neu gymwysiadau eraill, ni allwch ddibynnu'n llwyr ar hunan-reoleiddio'r nodwedd hon. Mae angen rhai mesurau sylfaenol o hyd. Mae'r nodwedd hon hefyd yn esbonio bod colledion dargludiad yn dod yn fwy ar dymheredd uchel. Felly, dylid rhoi sylw arbennig i ddewis paramedrau wrth gyfrifo colledion.

4. Bydd nodweddion cyfernod tymheredd negyddol ID, dealltwriaeth o baramedrau MOSFET a'i brif nodweddion ID yn gostwng yn sylweddol wrth i dymheredd y gyffordd gynyddu. Mae'r nodwedd hon yn ei gwneud hi'n aml yn angenrheidiol ystyried ei baramedrau ID ar dymheredd uchel yn ystod y dyluniad.

5. Nodweddion cyfernod tymheredd negyddol gallu eirlithriadau IER/EAS. Ar ôl i dymheredd y gyffordd gynyddu, er y bydd gan y MOSFET V(BR) DSS mwy, dylid nodi y bydd yr EAS yn cael ei leihau'n sylweddol. Hynny yw, mae ei allu i wrthsefyll eirlithriadau o dan amodau tymheredd uchel yn llawer gwannach nag ar dymheredd arferol.

6. Nid yw gallu dargludiad a pherfformiad adfer gwrthdro'r deuod parasitig yn y MOSFET yn well na gallu deuodau cyffredin. Ni ddisgwylir iddo gael ei ddefnyddio fel y prif gludwr cyfredol yn y ddolen yn y dyluniad. Mae deuodau blocio yn aml yn cael eu cysylltu mewn cyfres i annilysu'r deuodau parasitig yn y corff, a defnyddir deuodau cyfochrog ychwanegol i ffurfio cludwr trydanol cylched. Fodd bynnag, gellir ei ystyried fel cludwr yn achos dargludiad tymor byr neu rai gofynion cyfredol bach megis cywiro cydamserol.

7. Gall cynnydd cyflym potensial y draen achosi i'r gyriant gât ysgogi annilys, felly mae angen ystyried y posibilrwydd hwn mewn cymwysiadau DVDS/dt mawr (cylchedau switsio cyflym amledd uchel).